Рис. %img:n32_0

| [Home] | [Donate!] [Контакты] |

| [<< Тактовые сигналы микроконтроллеров STM32F100xx] | [Таймеры в микроконтроллерах STM >>] |

Цифро-аналоговый преобразователь - устройство, которое преобразует заданное на входе в цифровой форме число в соответствующее ему напряжение на своём аналоговом выходе.

Может использоваться в системах автоматического регулирования, измерительных системах, в качестве генератора сигналов произвольной формы и т.д. DAC в микроконтроллерах STM32F100xx имеют достаточно высокое разрешение и быстродействие для использования в аудио-приложениях (системы с голосовым оповещением; говорящие игрушки; беспроводная гарнитура; может быть, даже плееры низшей ценовой категории).

ОглавлениеМикроконтроллеры STM32F100xx имеют встроенный модуль цифро-аналогового преобразования (ЦАП, он же DAC: Digital-to-analog converter) с разрешением 12 бит. Модуль имеет два выходных канала, каждый из которых имеет собственный преобразователь, т.е. DAC модуль включает в себя два DAC преобразователя. Два канала могут работать независимо (также можно задействовать только один из каналов) или совместно, синхронно обновляя сигнал на выходе. Присутствует поддержка DMA для каждого канала. Есть несколько режимов запуска преобразования: автоматически при загрузке данных в DAC (по умолчанию); по программному сигналу; по таймеру; по сигналу с вывода микроконтроллера.

Дополнительно имеется возможность работать в режиме генерации сигнала треугольной формы или в режиме генерации шума.

DAC использует следующие выводы

VDDA: вход для аналогового питания. Потенциал на выводе аналогового питания должен быть тем же самым, что и на основных выводах питания VDD, иначе говоря вывод VDDA должен быть подключён к VDD, возможно, через дополнительный фильтр. Цепи питания разделены для уменьшения влияния помех, создаваемых цифровыми элементами микроконтроллера на аналоговые.

Если аналоговые устройства микроконтроллера не используются, то напряжение питания может быть в пределах 2..3.6 В, но если используется DAC или ADC, требуется, чтобы напряжение питания (VDD и VDDA) было в пределах 2.4..3.6 В.

VREF+: вход для опорного положительного напряжения DAC; опорные напряжения определяют диапазон возможных напряжений на выходе преобразователя. Напряжение на выходе преобразователя линейно зависит от преобразуемого цифрового кода, при изменении цифрового кода от 0 до максимально возможного (0x0FFF в случае разрядности 12 бит) на выходе преобразователя получим напряжения от VREF- до VREF+. Вывод VREF- доступен только в 100-выводных корпусах семейства STM32F100xx, в остальных он подключён к выводу VSSA (общий аналоговый). Но даже если вывод VREF- имеется, всё равно требуется, чтобы он был подключён к VSSA. Поэтому на самом деле выходное напряжение DAC может изменяться в пределах 0..VREF+.

Вывод VREF+ доступен только в микроконтроллерах в 100-выводных корпусах и в корпусе TFBGA64 (с матрицей 8*8 жёстких шариковых выводов). Должен быть подключен к источнику опорного напряжения от 2.4 В до VDDA.

В остальных корпусах VREF+ подключается к VDDA внутри микроконтроллера, т.е. в качестве опорного напряжения для DAC используется напряжение аналогового питания.

Прежде чем начать работу с периферийным устройством, следует включить для него тактовый сигнал. Для DAC, который подключён к шине APB1 это делают с помощью кода:

// Включаем тактовый сигнал DAC.

RCC->APB1ENR|=RCC_APB1ENR_DACEN;

После этого следует сконфигурировать выводы используемых каналов как аналоговые входы. Вывод PA4 используется как выход первого канала, вывод PA5 - второго. Кстати, раз используется порт ввода-вывода общего назначения GPIOA, то тактовый сигнал должен быть включён и для него.

После установки соответствующего каналу бита ENx в регистре управления DAC_CR, аналоговый выход канала будет подключён к выводу микроконтроллера. На включение требуется время tWAKEUP до 10 мкс (максимальное значение при условии, что ёмкость нагрузки CLOAD≤50 пф, сопротивление нагрузки RLOAD≥5 кОм; типичное значение: 6.5 мкс).

// Включаем тактовый сигнал GPIOA.

RCC->APB2ENR|=RCC_APB2ENR_IOPAEN;

// Конфигурируем выводы используемых каналов как аналоговые входы;

// в данном случае используем оба канала (выводы PA4, PA5).

// CNF=00, MODE=00

GPIOA->CRL&=~(0xFF<<4*4);

// Включаем оба канала. После установки бита требуется до 10 мкс

// для включения канала.

DAC->CR|=DAC_CR_EN1|DAC_CR_EN2;

DAC содержит два выходных буфера которые используются для уменьшения выходного сопротивления преобразователя, что позволяет подключать нагрузку без использования внешнего операционного усилителя. Буфер каждого канала может быть независимо включён и отключён с помощью битов BOFFx регистра DAC_CR. По умолчанию буферы включены. Устанавливая бит BOFFx, отключаем буфер канала x.

// Отключить буфер первого канала.

DAC->CR|=DAC_CR_BOFF1;

// Включить.

DAC->CR&=~DAC_CR_BOFF1;

Когда буфер отключен, выходное сопротивление канала может достигать 15 кОм. Для получения точности преобразования 1%, сопротивление нагрузки (между DAC_OUT и VSS) должно быть не меньше 1.5 МОм. При включённом буфере требования к нагрузке куда более мягкие, сопротивление нагрузки должно быть от 5 кОм или выше, а ёмкость - не более 50 пФ.

С другой стороны, при отключённом буфере на выходе преобразователя можно получить напряжение из полного диапазона 0..VREF+. Буфер же обеспечивает работу только с сигналами в диапазоне 0.2 В..VDDA-0.2 В.

Если требуется получить одновременно полный диапазон выходных напряжений и малое выходное сопротивление, следует отключить внутренний буфер и использовать внешний повторитель на операционном усилителе. Существуют операционные усилители, которые могут работать при однополярном питании, они включают потенциалы земли и питания в допустимые диапазоны входных и выходных напряжений. Но, как правило, лучшие результаты по линейности и нагрузочной способности могут быть достигнуты при двухполярном питании усилителя.

DAC микроконтроллеров STM32F100xx является 12-битным, однако поддерживается загрузка данных в нескольких форматах. Возможны три варианта:

В зависимости от используемого для загрузки регистра DAC_DHRyyyx, записанные пользователем данные автоматически сдвигаются (если нужно) и сохраняются в соответствующем регистре для хранения данных DHRx (сам регистр DHRx - внутренний и непосредственно недоступен, так как не отображается в пространство памяти). Затем содержимое DHRx загружается в регистр DORx - автоматически, по команде программы или по внешнему сигналу.

| 31 | 23 | 15 | 7 | 0 | ||

| 8 бит, выравнивание вправо | ||||||

| 12 бит, выравнивание влево | ||||||

| 12 бит, выравнивание вправо | ||||||

12-битный формат с выравниванием вправо - естественный формат для данного DAC, если используется этот формат, данные попадают в регистр DORx в неизменном виде.

12-битный формат со выравниванием влево позволяет загружать в DAC данные как 16-битные числа. При этом преобразователь, естественно, остаётся 12-битным, так что младшие 4 бита в загружаемых числах не учитываются (теряются при сдвиге вправо на 4 бита перед сохранением во внутреннем регистре).

8-битовый формат позволяет работать с 12-битным DAC преобразователем как с 8-битным устройством. Это может быть полезно в тех случаях, когда не требуется высокое разрешение преобразователя, но требуется сэкономить используемую память.

Кроме того, можно загрузить данные одновременно в два канала. В двухканальном режиме также возможны 3 варианта.

В зависимости от используемого для загрузки данных регистра DAC_DHRyyyD, загруженные пользователем данные автоматически сдвигаются (если необходимо) и сохраняются во внутренних, не отображаемых на пространство памяти регистрах DHR1 и DHR2. Затем содержимое DHR1 и DHR2 загружается в соответствующие регистры DOR1 и DOR2 - автоматически, программно или по внешнему сигналу.

| 31 | 23 | 15 | 7 | 0 | ||||

| 8 бит, выравнивание вправо | ||||||||

| 12 бит, выравнивание влево | ||||||||

| 12 бит, выравнивание вправо | ||||||||

Итак, для загрузки данных в DAC, в зависимости от того, какой формат данных хотим использовать, мы должны выполнить запись в один из регистров с именем вида DAC_DHRxyz, где x=8 или 12 - количество бит данных; y=L или R - определяет выравнивание влево (Left) или вправо (Right), для 8-битных данных может быть только выравнивание вправо; z=1, 2 или D - определяет, загружаются ли данные в регистр первого канала, второго, или загружаемое слово содержит данные для двух каналов.

Регистр DAC_DORx, который непосредственно связан с аналого-цифровым преобразователем и определяет напряжение на выходе канала DAC, недоступен для прямой записи. Вместо этого следует загрузить данные в один из регистров: DAC_DHR8Rx, DAC_DHR12Lx, DAC_DHR12Rx, DAC_DHR8RD, DAC_DHR12LD или DAC_DHR12LD.

Записанные в DAC_DHRx данные автоматически передаются в DAC_DORx через 1 цикл тактового сигнала APB1, если не выбран вариант аппаратного запуска преобразования (аппаратный запуск выбирается установкой бита TENx в регистре DAC_CR). Если аппаратный запуск выбран и сигнал запуска получен, передача данных в регистр DAC_DORx произойдёт через 3 такта тактового сигнала APB1.

После того, как в DAC_DORx будет загружено значение из DAC_DHRx, требуется время tSETTLING для установки напряжения на аналоговом выходе. Это время зависит от напряжения питания и нагрузки выхода DAC.

Если сопротивление и ёмкость нагрузки отвечает требованиям RLOAD≥5 кОм, CLOAD≤50 пФ, то время установки выходного напряжения с точностью ±1LSB не превышает 4 мкс (3 мкс - типичное значение) при изменении регистра от минимального (0) до максимального значения. В случае малых изменений, например при изменении значения регистра DOR на соседнее значение (±1), требуется существенно меньшее время для установки выходного напряжения. В документации на микроконтроллеры STM32F100xx указывается максимальная частота 1 MS/s (1.0e6 сэмплов в секунду), на которой DAC ещё обеспечивает корректный сигнал на выходе при малых изменениях значения DOR.

Цифровой код на входе DAC линейно преобразуется в выходное напряжение из диапазона 0..VREF+. Напряжение на аналоговом выводе канала DAC определяется соотношением

DACoutput=VREF+*DOR/4095.

По умолчанию преобразование цифрового кода в напряжение на выходе при включённом DAC осуществляется автоматически. В этом случае при изменении содержимого регистра DAC_DHRx (как изменить его содержимое описано выше, сам регистр недоступен для записи), через 1 такт тактового сигнала шины APB1 новое значение из DAC_DHRx копируется в DAC_DORx, а содержимое регистра DAC_DORx непосредственно определяет напряжение на выходе преобразователя.

Однако, есть возможность осуществлять пересылку содержимого из DAC_DHRx в DAC_DORx по внешнему сигналу. Это позволяет осуществить точную привязку аналогового сигнала к определённым моментам времени. Для этого с помощью битов TSELx[2:0] регистра DAC_CR определяют, какое событие будет запускать преобразование. Источник запуска может быть выбран только при выключенном канале DAC. С помощью бита TENx регистра DAC_CR включают режим преобразования по внешнему событию.

| Источник | Тип | TSEL[2:0]1 |

|---|---|---|

| Timer 6 TRGO event | Внутренние сигналы от таймеров микроконтроллера | 000 |

| Timer 3 TRGO event | 001 | |

| Timer 7 TRGO event | 010 | |

| Timer 5 или Timer 15 TRGO event2 | 011 | |

| Timer 2 TRGO event | 100 | |

| Timer 4 TRGO event | 101 | |

| EXTI line9 | Внешний вывод микроконтроллера | 110 |

| SWTRIG | Устанавливаемый программно бит SWTRIGx регистра DAC_SWTRIGR | 111 |

Каждый раз при обнаружении нарастающего фронта на выходе TRGO выбранного таймера или в случае внешнего прерывания по линии 9, данные, сохранённые в регистре DAC_DHRx пересылаются в регистр DAC_DORx. Содержимое DAC_DORx обновляется через 3 такта тактового сигнала на шине APB1 после того, как событие запуска произошло.

Если выбран программный запуск, преобразование запускается при установке бита SWTRIG. Этот бит сбрасывается аппаратно после того, как в регистр DAC_DORx будет загружено значение из DAC_DHRx. В данном случае на обновление регистра DAC_DORx требуется 1 такт тактового сигнала на шине APB1.

Примечание.

1. Биты TSELx[2:0] не могут быть изменены при установленном бите ENx.

2. В микроконтроллерах из линейки high-density value line (устройства с объёмом Flash памяти от 256 до 512 Кб) при выборе TSEL=3 запуск по умолчанию происходит по событию TRGO таймера TIM5, но с помощью функций переназначения AFIO может быть задействован таймер TIM15. В линейках low- и medium-density (объём Flash памяти 16..32 Кб и 64..128 Кб) при выборе источника запуска преобразования TSEL=3, всегда используется TIM15.

// Простейшая программа для STM32F100RB или совместимого,

// демонстрирующая использование DAC устройства микроконтроллера.

// На выходе канала 1 (PA4) формирует фиксированное напряжение,

// на выходе канала 2 (PA5) формирует синусоидальное колебание.

/**

* IMPORTANT NOTE!

* The symbol VECT_TAB_SRAM needs to be defined when building the project

* if code has been located to RAM and interrupts are used.

* Otherwise the interrupt table located in flash will be used.

* See also the <system_*.c> file and how the SystemInit() function updates

* SCB->VTOR register.

* E.g. SCB->VTOR = 0x20000000;

*/

#include <stm32f10x.h>

#include <math.h> // Используем M_PI, sinf

int main()

{

// Включаем тактовый сигнал DAC.

RCC->APB1ENR|=RCC_APB1ENR_DACEN;

// Включаем тактовый сигнал GPIOA.

RCC->APB2ENR|=RCC_APB2ENR_IOPAEN;

// Конфигурируем выводы используемых каналов как аналоговые входы;

// в данном случае используем оба канала (выводы PA4, PA5).

// CNF=00, MODE=00

GPIOA->CRL&=~(0xFF<<4*4);

// Включаем оба канала. После установки бита требуется до 10 мкс

// для включения канала.

DAC->CR|=DAC_CR_EN1|DAC_CR_EN2;

// ********************************************

// Простейшие примеры использования DAC.

// Предполагаем, что напряжение питания: 3.3 В.

// ********************************************

// Вычисление цифрового кода для напряжения u на выходе DAC.

#define dhr(u) ((int32_t)((4095/3.3)*(u)))

// Устанавливаем напряжение на выходе канала 1,

// можем контролировать результат вольтметром (вывод PA4).

DAC->DHR12R1=dhr(1.234);

// Запускаем системный таймер.

// Обработчик исключения от системного таймера формирует

// периодический сигнал на выходе второго канала.

// Можем проконтролировать результат с помощью осциллографа (вывод PA5).

SysTick_Config(SystemCoreClock/1000);

while(true);

}

// Обработчик исключения от системного таймера

// (в данной программе таймер настроен на генерацию исключений каждую мс).

extern "C" void SysTick_Handler()

{

// На выходе канала 2 формируем ступенчатое приближение к синусоиде:

// постоянное смещение 1.6 В; амплитуда 1 В; N точек на период.

// (при частоте отсчётов 1000 Гц - частота сигнала 1000/N).

// u=a0+a1*sin(2*pi*t/T); t=1ms*tick=0.001*tick, tick - порядковый

// номер данного отсчёта; T=1/f=N/1000 ==>

// u=a0+a1*sin(2*pi*tick/N)

static int tick=0;

const int N=20;

const int a0=dhr(1.6);

const int a1=dhr(1);

const float w=2*M_PI/N;

// Используется синтез сигнала на "лету".

// Лучшие результаты по быстродействию могут быть получены

// при использовании предвычисленной таблицы.

DAC->DHR12R2=a0+(int32_t)(a1*sinf(w*tick));

tick++;

if(tick>=N)

tick=0;

}

Прежде всего надо признать, что это, конечно, плохой пример и синтезировать сигнал таким способом не следует. Во-первых, кроме исключения от системного таймера обычно бывает разрешена обработка и других исключений. Тогда исключение от системного таймера, как правило, имеющее низкий приоритет может быть отложено, если в данный момент выполняется обработка других исключений. Хуже всего то, что моменты возникновения задержки и их длительность непредсказуемы. В результате в формируемый сигнал будут вноситься случайные фазовые искажения. Во-вторых, даже если бы не было "во-первых", длительность вычислений, производимых с числами с плавающей точкой будет немного изменяться при изменении операндов (потому что код, реализующий эмуляцию операций с плавающей точкой содержит операторы ветвления; в зависимости от выбора ветвей в процессе вычислений, количество выполненных операторов будет отличаться). Второй эффект легко устраним, если немного модифицировать код: сначала пишем в регистр DAC значение, вычисленное во время предыдущей обработки исключения от таймера, а уже после этого вычисляем новое значение, которое будет использоваться в следующий раз.

Но лучше воспользоваться возможностью аппаратного запуска преобразования по событию, например по сигналу таймера. Вопросам "правильного" синтеза сигналов посвящена серия статей, начиная с "Микроконтроллер + DAC как синтезатор сетки частот" и далее.

В нашем примере, для вычисления мгновенных значений сигнала при генерации синусоиды, используется функция sinf - float вариант функции sin. Если использовать функцию sin, работающую с числами типа double, то получим чрезмерную точность, совершенно излишнюю для 12-битного ADC. Кроме того, двоичный код программы получится слишком большим для отладки в RAM-памяти.

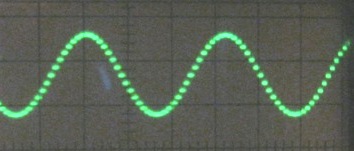

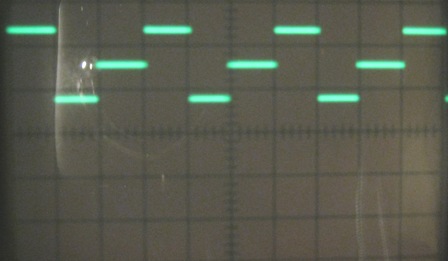

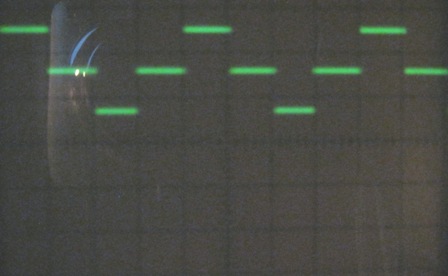

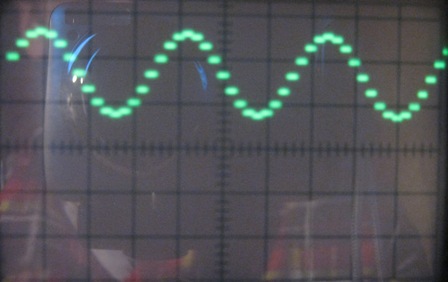

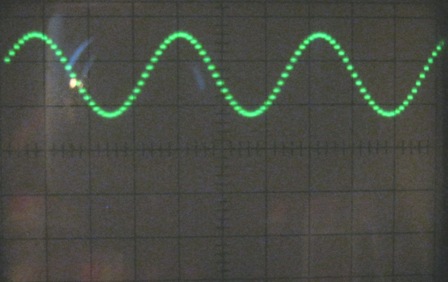

На выходе второго канала получается ступенчатый сигнал - приближение к синусоиде, имеющее большую или меньшую точность. Далее приведены изображения получаемых сигналов при N=3, 4, 8, 16 и 32. Так как фотографии получены с аналогового осциллографа, видны только горизонтальные линии ступенек, на вертикальных (точнее, почти вертикальных) участках скорость движения луча осциллографа слишком высока, чтобы оставлять заметный след на экране.

Рис. %img:n3. N=3; Y: 1 В/дел.; X: 1 мс/дел. Это ещё совсем не похоже на синусоиду.

Рис. %img:n4. N=4; Y: 1 В/дел.; X: 1 мс/дел.

Рис. %img:n16. N=16; Y: 1 В/дел.; X: 5 мс/дел.

Рис. %img:n32. N=32; Y: 1 В/дел.; X: 10 мс/дел.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | |

| Reserved | DMAU DRIE2 |

DMA EN2 |

MAMP2[3:0] | WAVE2[1:0] | TSEL2[2:0] | TEN2 | BOFF2 | EN2 | ||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | |||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| Reserved | DMAU DRIE1 |

DMA EN1 |

MAMP1[3:0] | WAVE1[1:0] | TSEL1[2:0] | TEN1 | BOFF1 | EN1 | ||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | |||

Address offset: 0x00

Reset value: 0x0000 0000

Этот 32-битовый регистр управляет настройками DAC. Младшая половина регистра определяет конфигурацию первого канала, старшая - второго. Поскольку обе половины регистра идентичны, укажем назначение битов только для первого канала.

DMAUDRIE1: DAC channel1 DMA Underrun Interrupt enable

Бит устанавливается и сбрасывается программно; значение 1 разрешает генерацию прерывания в случае ошибки DMA Underrun, 0 запрещает прерывание.

DMAEN1: DAC channel1 DMA enable

Бит устанавливается и сбрасывается программно; значение 1 включает режим DMA, 0 отключает.

MAMP1[3:0]: DAC channel1 mask/amplitude selector

Битовое поле, записываемое программно. Используется, если включён один из режимов аппаратной генерации (реализованы генерация псевдошума или генерация треугольных колебаний). Определяет используемую маску в режиме генерации шума и амплитуду в режиме генерации треугольных импульсов.

0000: бит 0 регистра LFSR не маскируется / амплитуда треугольных колебаний 1;

0001: биты [1:0] регистра LFSR не маскируется / амплитуда треугольных колебаний 3;

...

1011: биты [11:0] регистра LFSR не маскируется / амплитуда треугольных колебаний 4095;

т.е., в общем случае, если битовое поле MAMP1[3:0] содержит значение n, где n=0..11, то:

n: биты [n:0] регистра LFSR не маскируется / амплитуда треугольных колебаний 2**(n+1)-1,

здесь оператор "**" означает возведение в степень.

WAVE1[1:0]: DAC channel1 noise/triangle wave generation enable

Битовое поле, изменяемое программно. Позволяет включить один из поддерживаемых аппаратно режимов генерации.

00: режим генерации отключён;

01: включён режим генерации шума;

1x: включён режим генерации треугольных колебаний.

Примечание. Используется только если бит TEN1=1.

TSEL1[2:0]: DAC channel1 trigger selection

Битовое поле, устанавливаемое программно и позволяющее выбрать, какое внешнее по отношению к DAC событие будет запускать процесс преобразования.

000: Timer 6 TRGO event;

001: Timer 3 TRGO event;

010: Timer 7 TRGO event;

011: Timer 5 или Timer 15 TRGO event;

100: Timer 2 TRGO event;

101: Timer 4 TRGO event;

110: External line9;

111: программный запуск (запуск при программной установке в 1 бита SWTRIG1 в регистре DAC_SWTRIGR).

Примечание. Используется только если бит TEN1=1.

TEN1: DAC channel1 trigger enable

Бит устанавливается и сбрасывается программно для включения/отключения запуска преобразования от внешнего события.

0: запуск по событию отключён для канала 1 и записанные в регистр DAC_DHR1 данные передаются в регистр DAC_DOR1 через 1 такт тактового сигнала шины APB1.

1: включён запуск преобразования по событию, источник которого определяется битами TSEL1[2:0]. После возникновения события, данные из DAC_DHR1 через 3 такта тактового сигнала APB1 передаются в DAC_DOR1, а когда выбран вариант программного запуска - требуется только 1 такт для передачи.

BOFF1: DAC channel1 output buffer disable

Устанавливаемый и сбрасываемый программно бит для отключения/включения выходного буфера канала.

0: буфер включен (по умолчанию буфер включен);

1: буфер отключён.

Примечание. Подробнее о преимуществах и недостатках использования буфера было сказано ранее в этой статье.

EN1: DAC channel1 enable

Бит устанавливается и сбрасывается программно, используется для включения канала 1 преобразователя DAC.

0: канал 1 отключён;

1: канал 1 включён.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | |

| Reserved | ||||||||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| Reserved | SWTRIG2 | SWTRIG1 | ||||||||||||||

| w | w | |||||||||||||||

Address offset: 0x04

Reset value: 0x0000 0000

SWTRIG2, SWTRIG1: DAC channel2/channel1 software trigger

Бит SWTRIGx устанавливается программно в 1 для программного запуска процесса преобразования, если DAC сконфигурирован для работы в этом режиме (заданы значения TSELx[2:0]=7, TENx=1). Бит сбрасывается в 0 аппаратно после загрузки значения из DAC_DHRx в DAC_DORx.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | |

| Reserved | ||||||||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| Reserved | DACC1DHR[11:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | |||||

Address offset: 0x08

Reset value: 0x0000 0000

Регистр предназначен для записи 12-битовых данных, выровненных вправо для первого канала DAC.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | |

| Reserved | ||||||||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| DACC1DHR[11:0] | Reserved | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | |||||

Address offset: 0x0C

Reset value: 0x0000 0000

Регистр предназначен для записи 12-битовых данных первого канала DAC, выровненных влево.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | |

| Reserved | ||||||||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| Reserved | DACC1DHR[7:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | |||||||||

Address offset: 0x10

Reset value: 0x0000 0000

Регистр предназначен для записи 8-битовых данных первого канала DAC, выровненных вправо.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | |

| Reserved | ||||||||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| Reserved | DACC2DHR[11:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | |||||

Address offset: 0x14

Reset value: 0x0000 0000

Регистр предназначен для записи 12-битовых данных, выровненных вправо для второго канала DAC.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | |

| Reserved | ||||||||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| DACC2DHR[11:0] | Reserved | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | |||||

Address offset: 0x18

Reset value: 0x0000 0000

Регистр предназначен для записи 12-битовых данных второго канала DAC, выровненных влево.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | |

| Reserved | ||||||||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| Reserved | DACC2DHR[7:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | |||||||||

Address offset: 0x1C

Reset value: 0x0000 0000

Регистр предназначен для записи 8-битовых данных второго канала DAC, выровненных вправо.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | |

| Reserved | DACC2DHR[11:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | |||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| Reserved | DACC1DHR[11:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | |||||

Address offset: 0x20

Reset value: 0x0000 0000

Регистр предназначен для программной записи данных в формате 12 бит (выравнивание вправо) сразу для обоих каналов DAC.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | |

| DACC2DHR[11:0] | Reserved | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | |||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| DACC1DHR[11:0] | Reserved | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | |||||

Address offset: 0x24

Reset value: 0x0000 0000

Регистр предназначен для программной записи данных в формате 12 бит (выравнивание влево) сразу для обоих каналов DAC.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | |

| Reserved | ||||||||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| DACC2DHR[7:0] | DACC1DHR[7:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | |

Address offset: 0x28

Reset value: 0x0000 0000

Регистр предназначен для программной записи данных в формате 8 бит (в случае 8 бит поддерживается только выравнивание вправо) сразу для обоих каналов DAC.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | |

| Reserved | ||||||||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| Reserved | DACC1DOR[11:0] | |||||||||||||||

| r | r | r | r | r | r | r | r | r | r | r | r | |||||

Address offset: 0x2C

Reset value: 0x0000 0000

Регистр только для чтения, содержит выходные данные, преобразуемые первым каналом DAC. Содержимое регистра определяет выходное напряжение преобразователя: DACoutput1=VREF+*DAC_DOR1/4095.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | |

| Reserved | ||||||||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| Reserved | DACC2DOR[11:0] | |||||||||||||||

| r | r | r | r | r | r | r | r | r | r | r | r | |||||

Address offset: 0x30

Reset value: 0x0000 0000

Регистр только для чтения, содержит выходные данные, преобразуемые вторым каналом DAC. Содержимое регистра определяет выходное напряжение преобразователя: DACoutput2=VREF+*DAC_DOR2/4095.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | |

| Reserved | DMAUDR2 | Reserved | ||||||||||||||

| rc_w1 | ||||||||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| Reserv | DMAUDR1 | Reserved | ||||||||||||||

| rc_w1 | ||||||||||||||||

Address offset: 0x34

Reset value: 0x0000 0000

DMAUDR2, DMAUDR1: DAC channel2/channel1 DMA underrun flag.

Бит устнавливается в 1 аппаратно при возникновении ошибки DMA underrun соответственно во втором и первом канале DAC. Сброс бита в 0 осуществляется записью в него 1.