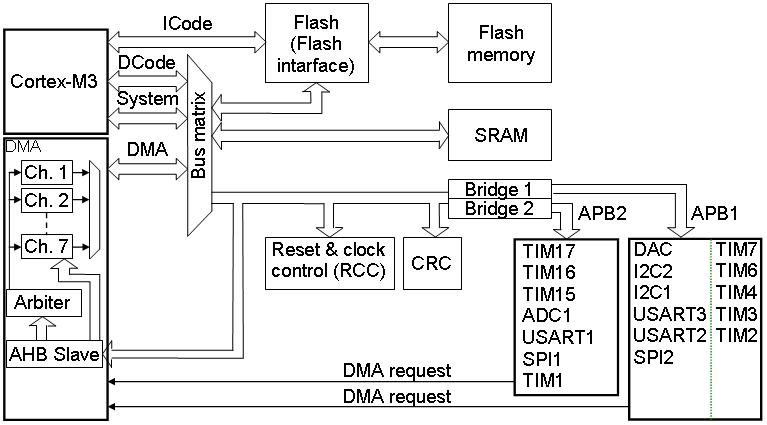

Рис. %img:i1

| [Home] | [Donate!] [Контакты] |

| [<< Использование базовых таймеров (TIM6, TIM7)] | [Микроконтроллер + DAC как синтезатор сетки частот >>] |

Зачастую при выполнении программ, значительная часть процессорного времени затрачивается на копирование данных из одной области памяти в другую. Ещё с большими затратами связано обслуживание периферийных устройств, особенно когда требуется загрузку/чтение данных точно привязывать к определённым моментам времени или событиям.

Использование механизмов DMA позволяет получить двойной выигрыш. Во-первых, при пересылке данных с помощью DMA можно достичь очень высоких скоростей передачи информации. Во-вторых, DMA освобождает процессор от рутинных операций копирования данных и пересылки данных между периферией и памятью по запросам периферийных устройств, в это время процессор может выполнять другую важную работу.

Кроме того, несмотря на богатство возможностей, работа с DMA реализуется весьма просто. Программа, использующая DMA, может получиться не только быстрее, но и проще чем программа, не использующая этих возможностей. В данном документе рассмотрим устройство, возможности и использование DMA в микроконтроллерах STM32F100xx.

ОглавлениеDMA (direct memory access), прямой доступ к памяти, используется для обеспечения высокоскоростной передачи данных между периферийными устройствами и памятью, а также для копирования данных из одной области памяти в другую. Процесс пересылки данных с помощью DMA не требует каких-либо действий от процессора и освобождает его ресурсы для выполнения других операций.

Микроконтроллеры STM32F100xx имеют один или два контроллера DMA, которые предоставляют в наше распоряжение до 12 каналов DMA (7 каналов имеет DMA1 и 5 каналов - DMA2), каждый из которых выделен для обслуживания запросов на доступ к памяти от одного или нескольких периферийных устройств. DMA имеет устройство-арбитр, которое отвечает за учёт приоритетов при обработке запросов.

Контроллер DMA выполняет передачу данных с прямым доступом к памяти, разделяя системную шину для совместного использования с ядром Cortex-M3. DMA запрос может задержать доступ процессора к системной шине на несколько тактов в случае, если процессор и контроллер DMA адресуют одного и того же получателя данных (память или периферийное устройство). Шинная матрица реализует круговое планирование, что гарантирует, по меньшей мере, предоставление процессору половины полосы пропускания системной шины (для доступа как к памяти, так и к периферии).

На рис. %img:i1 изображена блок-схема контроллера DMA1 микроконтроллеров семейств Low density Value Line, Medium density Value Line (к ним относятся микроконтроллеры STM32F100xx, имеющие до 128 Кб Flash-памяти).

На рис. %img:i2 изображена блок-схема контроллеров DMA1, DMA2. Отметим, что устройства DMA2, SPI3, UART4, UART5, TIM5 среди микроконтроллеров STM32F100xx имеются только в устройствах семейства High density Value Line (к ним относятся устройства, имеющие от 256 до 512 Кб Flash-памяти, это микроконтроллеры STM32F100xx, где xx=RC, RD, RE, VC, VD, VE, ZC, ZD, ZE).

После возникновения события в периферийном устройстве, которое требует прямого доступа к памяти, посылается сигнал запроса в контроллер DMA (если периферийное устройство настроено на использование возможностей DMA). Контроллер обслуживает запрос с учётом приоритета каналов. Как только происходит обращение контроллера DMA к периферийному устройству, контроллер посылает ему сигнал подтверждения. Периферийное устройство, получив подтверждение, сразу же снимает сигнал запроса DMA, контроллер DMA в ответ на это снимает сигнал подтверждения. Если требуется, периферийное устройство может инициализировать следующую транзакцию.

Если обобщить, каждая передача с использованием DMA состоит из трёх операций:

Арбитр координирует DMA запросы в соответствии с приоритетами каналов и запускает последовательность обращений к периферии/памяти для обработки первоочередного в данной ситуации запроса.

Приоритет определяется на программном и аппаратном уровнях:

Каждый канал может управлять DMA передачей между регистром периферийного устройства, расположенного по фиксированному адресу и памятью. Количество элементов данных (байт, полуслов или слов), которые должны быть переданы, задаётся программно и может быть от 0 до 65535. Регистр, содержащий количество элементов для пересылки, декрементируется после каждой пересылки.

Программируемый размер данных. Размер одного элемента (1, 2 или 4 байта) устанавливается независимо не только для каждого канала, но и отдельно для источника и приёмника данных в каждом канале - с помощью битовых полей PSIZE и MSIZE регистра DMA_CCRx.

Инкремент адреса. Текущий указатель на данные источника/приёмника может оставаться неизменным после выполнения DMA транзакции (что требуется при работе с периферийными устройствами, так как они имеют регистры с фиксированными адресами), но можно настроить DMA на автоматическое увеличение указателя после выполнения транзакции. Это делается с помощью битов PINC и MINC регистра DMA_CCRx. При установленном бите, содержимое соответствующего указателя периферии/памяти будет автоматически увеличиваться на 1, 2 или 4, в зависимости от заданного размера элемента данных, в результате чего указатель будет перемещаться на следующий элемент данных. Адреса, используемые во время первой передачи данных, задаются регистрами DMA_CPARx/DMA_CMARx. В процессе выполнения операций передачи, их значения остаются неизменными. Текущие значения адресов хранятся во внутренних регистрах микроконтроллера и недоступны программно.

Если канал сконфигурирован для работы в нециклическом режиме, DMA запросы по этому каналу не будут обслуживаться после выполнения последней передачи данных (когда регистр, содержащий количество элементов для пересылки достигает 0). Для загрузки нового количества пересылаемых элементов в регистр DMA_CNDTRx, необходимо предварительно отключить DMA канал. При отключении канала DMA, его регистры не сбрасываются (DMA_CCRx, DMA_CPARx and DMA_CMARx сохраняют значения, заданные в процессе предшествующего конфигурирования канала).

В циклическом режиме, после выполнения последней пересылки, в регистр DMA_CNDTRx автоматически загружается первоначально заданное значение, а внутренние регистры текущих адресов перезагружаются значениями базовых адресов из регистров DMA_CPARx/DMA_CMARx. Обслуживание DMA запросов продолжается.

Для настройки канала с номером x в контроллере DMA, необходимо выполнить следующую последовательность действий.

После включения канала, начнётся обслуживание DMA запросов от периферийного устройства, подключённого к каналу.

После того, как будет выполнена пересылка половины от заданного общего количества элементов, будет установлен флаг HTIF, а если установлен разрешающий прерывание бит HTIE, то произойдёт прерывание. Когда будет выполнена пересылка всех данных, будет установлен флаг TCIF и произойдёт прерывание, если оно разрешено установкой бита TCIE. При работе в нециклическом режиме, после пересылки заданного количества элементов, обслуживание DMA запросов для данного канала прекращается.

Если битом CIRC регистра DMA_CCRx включён циклический режим работы, то после завершения передачи данных регистр, содержащий количество элементов для пересылки перезагружается своим первоначальным значением и обслуживание запросов продолжается. Этот режим хорошо подходит для работы с кольцевыми буферами и непрерывными потоками данных (например, получение данных от ADC, работающего в режиме непрерывного преобразования).

DMA каналы могут также работать без запуска по запросу от периферии. Это происходит в режиме memory-to-memory, который включается установкой бита MEM2MEM в регистре DMA_CCRx. Если этот бит установлен, передача данных начинается сразу после программной установки бита включения EN в регистре DMA_CCRx.

Пересылка завершается при достижении регистром DMA_CNDTRx значения 0. Режим не может использоваться одновременно с циклическим режимом.

В размещённой ниже таблице приведены примеры разных вариантов пересылки с использованием DMA со всеми возможными сочетаниями размеров элементов данных приёмника и источника. Пересылка осуществляется по схеме элемент в элемент, т.е. считывается один элемент данных из источника данных, преобразуется к размеру элемента данных приёмника и пересылается по месту назначения. Порядок битов при пересылке сохраняется. Если элемент приёмника имеет размер больше, чем элемент данных источника, то недостающие старшие биты заполняются нулями. Если размер элемента в приёмнике меньше, чем в источнике, старшие биты данных отбрасываются.

Обозначения столбцов:

Src width - размер одного элемента данных источника в битах.

Dst Width - размер одного элемента данных приёмника в битах.

NDT (Number of data items to transfer) - количество элементов данных для пересылки в данном примере.

Src addr/data - адрес и данные источника (адрес даётся в виде смещения относительно базового значения в форме: @смещение).

Dst addr/data - адрес приёмника и данные, помещённые в него после завершения передачи.

Transfer operations - операции, выполняемые в процессе перемещения (что и откуда читается; что и откуда записывается), в результате которых получаем конечное содержимое приёмника.

| Src width |

Dst width |

NDT | Src addr/data |

Dst |

Transfer operations |

| 8 | 8 | 4 |

@0x0 / B0 @0x1 / B1 @0x2 / B2 @0x3 / B3 |

@0x0 / B0 |

1: READ B0[7:0] @0x0 then WRITE B0[7:0] @0x0 2: READ B1[7:0] @0x1 then WRITE B1[7:0] @0x1 3: READ B2[7:0] @0x2 then WRITE B2[7:0] @0x2 4: READ B3[7:0] @0x3 then WRITE B3[7:0] @0x3 |

| 8 | 16 | 4 |

@0x0 / B0 |

@0x0 / 00B0 |

1: READ B0[7:0] @0x0 then WRITE 00B0[15:0] @0x0 |

| 8 | 32 | 4 |

@0x0 / B0 |

@0x0 / 000000B0 |

1: READ B0[7:0] @0x0 then WRITE 000000B0[31:0] @0x0 |

| 16 | 8 | 4 |

@0x0 / B1B0 |

@0x0 / B0 |

1: READ B1B0[15:0] @0x0 then WRITE B0[7:0] @0x0 |

| 16 | 16 | 4 |

@0x0 / B1B0 |

@0x0 / B1B0 |

1: READ B1B0[15:0] @0x0 then WRITE B1B0[15:0] @0x0 |

| 16 | 32 | 4 |

@0x0 / B1B0 |

@0x0 / 0000B1B0 |

1: READ B1B0[15:0] @0x0 then WRITE 0000B1B0[31:0] @0x0 |

| 32 | 8 | 4 |

@0x0 / B3B2B1B0 |

@0x0 / B0 |

1: READ B3B2B1B0[31:0] @0x0 then WRITE B0[7:0] @0x0 |

| 32 | 16 | 4 |

@0x0 / B3B2B1B0 |

@0x0 / B1B0 |

1: READ B3B2B1B0[31:0] @0x0 then WRITE B1B0[7:0] @0x0 |

| 32 | 32 | 4 |

@0x0 / B3B2B1B0 |

@0x0 / B3B2B1B0 |

1: READ B3B2B1B0[31:0] @0x0 then WRITE B3B2B1B0[31:0] @0x0 |

Когда DMA начинает операцию записи байта или полуслова в устройство на шине AHB, данные дублируются на неиспользуемых линиях шины HWDATA[31:0]. Так что, когда используется периферийное устройство на шине AHB, которое не поддерживает операций записи байт и полуслов (в том случае, если HSIZE не используется периферийным устройством) и не генерирует никаких ошибок, DMA записывает 32-битовые данные, как это показано в следующих примерах:

1) при записи полуслова 0xABCD, DMA устанавливает на шине HWDATA 0xABCDABCD и HSIZE=HalfWord;

2) при записи байта 0xAB, DMA устанавливает на шине HWDATA 0xABABABAB и HSIZE=Byte.

С учётом того, что AHB/APB мост является 32-битным подчинённым периферийным устройством на шине AHB, которое не учитывает HSIZE, любая операция с байтом или полусловом будет преобразована в 32-битовую операцию следующим образом:

AHB операция записи байта 0xB0 по адресу 0x0 (или 0x1, 0x2, 0x3) будет преобразована в APB операцию записи слова 0xB0B0B0B0 по адресу 0x0;

AHB операция записи полуслова 0xB1B0 по адресу 0x0 (или 0x2) будет преобразована в APB операцию записи слова 0xB1B0B1B0 по адресу 0x0.

Например, если требуется выполнить запись в APB backup регистр (16-битовый регистр с выравниванием адреса на 32-битовую границу), следует задать размер данных в источнике - памяти (MSIZE) равным 16 бит и размер данных в приёмнике - периферийном устройстве (PSIZE) равным 32 бита.

Ошибка в процессе пересылки данных с использованием DMA может возникнуть в результате попытки чтения или записи по адресу из зарезервированного адресного пространства. В таких случаях, вызвавший ошибку канал DMA автоматически отключается за счёт аппаратного сброса бита EN в соответствующем этому каналу конфигурационном регистре DMA_CCRx. Устанавливается флаг ошибки передачи TEIF в регистре DMA_IFR и генерируется прерывание DMA, если это разрешено установкой бита TEIE в регистре DMA_CCRx.

Прерывания могут генерироваться в результате установки флага HTIF, TCIF или TEIF, т.е. после завершения пересылки половины данных, всех данных или в случае возникновения ошибки соответственно. Для того чтобы разрешить генерацию прерывания при установке того или иного флага, используются биты HTIE, TCIE и TEIE.

Каждый канал имеет свой собственный вектор прерывания, за одним исключением: в семействе микроконтроллеров "high-density value line" каналы 4 и 5 контроллера DMA2 используют один и тот же вектор.

Количество DMA каналов ограничено, в связи с этим, каждый канал используется для подачи DMA запросов от нескольких периферийных устройств (сигналы от нескольких устройств на одном канале просто объединяются логической операцией ИЛИ). Поэтому одновременно только одно периферийное устройство на данном канале может использовать DMA. Для того чтобы иметь возможность включать/отключать использование функций DMA, каждое периферийное устройство с поддержкой прямого доступа в память имеет бит для активации/деактивации режима формирования запросов DMA. По умолчанию, после сброса микроконтроллера, формирование DMA запросов для всех периферийных устройств отключено.

На следующем рисунке изображена блок-схема, поясняющая отображение линий запроса DMA от периферийных устройств на каналы контроллера DMA1 (аналогичным образом организовано подключение устройств к каналам контроллера DMA2, если он имеется).

Отображение запросов на каналы DMA от устройств TIM1_CH1, TIM1_CH2, а в микроконтроллерах семейства high-density value line также и TIM6_DAC1, TIM7_DAC2, зависит от настроек AFIO. Подробнее об этом можно почитать в разделе документации, посвящённом AFIO.

Размещённая ниже таблица содержит полную информацию об отображении запросов DMA от периферийных устройств на каналы контроллера DMA.

| ПУ | Канал 1 | Канал 2 | Канал 3 | Канал 4 | Канал 5 | Канал 6 | Канал 7 |

|---|---|---|---|---|---|---|---|

| ADC1 | ADC1 | ||||||

| SPI | SPI1_RX | SPI1_TX | SPI2_RX | SPI2_TX | |||

| USART | USART3_TX | USART3_RX | USART1_TX | USART1_RX | USART2_RX | USART2_TX | |

| I2C | I2C2_TX | I2C2_RX | I2C1_TX | I2C1_RX | |||

| TIM1 | TIM1_CH1 | TIM1_CH2 | TIM1_CH4 TIM1_TRIG TIM1_COM |

TIM1_UP | TIM1_CH3 TIM1_CH2 TIM1_CH1 |

||

| TIM2 | TIM2_CH3 | TIM2_UP | TIM2_CH1 | TIM2_CH2 TIM2_CH4 |

|||

| TIM3 | TIM3_CH3 | TIM3_CH4 TIM3_UP |

TIM3_CH1 TIM3_TRIG |

||||

| TIM4 | TIM4_CH1 | TIM4_CH2 | TIM4_CH3 | TIM4_UP | |||

| TIM6/ DAC Ch1 |

TIM6_UP/ DAC_Channel1 |

||||||

| TIM7/ DAC Ch2 |

TIM7_UP/ DAC_Channel2 |

||||||

| TIM15 | TIM15_CH1 TIM15_UP TIM15_TRIG TIM15_COM |

||||||

| TIM16 | TIM16_CH1 TIM16_UP |

||||||

| TIM17 | TIM17_CH1 TIM17_UP |

Следующая таблица содержит информацию об отображении запросов DMA от периферийных устройств на каналы контроллера DMA2.

| ПУ | Канал 1 | Канал 2 | Канал 3 | Канал 4 | Канал 5 |

|---|---|---|---|---|---|

| SPI3 | SPI3_RX | SPI3_TX | |||

| UART4 | UART4_RX | UART4_TX | |||

| UART5 | UART5_TX | UART5_RX | |||

| TIM5 | TIM5_CH4 TIM5_TRIG |

TIM5_CH3 TIM5_UP |

TIM5_CH2 | TIM5_CH1 | |

| TIM6/ DAC_Ch1 |

TIM6_UP/ DAC_Channel1 |

||||

| TIM7/ DAC_Ch2 |

TIM7_UP/ DAC_Channel2 |

Доступ к регистрам можно выполнять как к байтам (8 бит), полусловам (16 бит) или словам (32 бита).

В используемых обозначениях под DMA подразумевается либо DMA1, либо DMA2, в зависимости от того, к регистру какого контроллера DMA мы хотим обратиться. В микроконтроллерах STM32F100xx семейств Low и Medium density Value Line имеется только DMA1 и всюду под DMA подразумевается DMA1.

Каждый канал DMA имеет либо свой регистр, либо своё битовое поле в общем регистре. Для обозначения номера канала будет использоваться символ "x", x=1..7 в случае DMA1 и x=1..5 для контроллера DMA2.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | |

| Reserved | TEIF7 | HTIF7 | TCIF7 | GIF7 | TEIF6 | HTIF6 | TCIF6 | GIF6 | TEIF5 | HTIF5 | TCIF5 | GIF5 | ||||

| r | r | r | r | r | r | r | r | r | r | r | r | |||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| TEIF4 | HTIF4 | TCIF4 | GIF4 | TEIF3 | HTIF3 | TCIF3 | GIF3 | TEIF2 | HTIF2 | TCIF2 | GIF2 | TEIF1 | HTIF1 | TCIF1 | GIF1 | |

| r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | |

Address offset: 0x00

Reset value: 0x0000 0000

Регистр состояния прерывания, содержит набор флагов (по 4 флага на канал DMA), которые устанавливаются аппаратно при наступлении соответствующего события. Установка любого из флагов может привести к генерации прерывания, если это разрешено. Сброс флагов осуществляется с помощью регистра DMA_IFCR (сброс необходим при обработке прерываний от DMA).

TEIFx: Channel x transfer error flag

Флаг ошибки передачи в канале x, этот бит устанавливается аппаратно. Сбрасывается записью 1 в соответствующий бит регистра DMA_IFCR.

0: Не было ошибок передачи в DMA канале x.

1: На канале x произошла ошибка при пересылке данных.

HTIFx: Channel x half transfer flag

Флаг завершения передачи половины данных в канале x, бит устанавливается аппаратно. Сбрасывается программно записью 1 в соответствующий бит регистра DMA_IFCR.

0: Не было события - завершения передачи половины от общего количества данных.

1: Было зафиксировано событие - завершение передачи половины данных.

TCIFx: Channel x transfer complete flag

Флаг завершения передачи в канале x, бит устанавливается аппаратно. Сбрасывается программно записью 1 в соответствующий бит регистра DMA_IFCR.

0: Не было зафиксировано события - завершения передачи данных.

1: Было зафиксировано событие - завершение передачи данных.

GIFx: Channel x global interrupt flag

Глобальный флаг прерывания в канале x, бит устанавливается аппаратно одновременно с установкой любого из флагов для данного канала: TEIFx, HTIFx или TCIFx. Сбрасывается программно записью 1 в соответствующий бит регистра DMA_IFCR.

0: Не происходило установки ни одного из флагов TEIFx, HTIFx или TCIFx на данном канале DMA.

1: Произошла установка одного из флагов TEIFx, HTIFx или TCIFx.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | |

| Reserved | CTEIF7 | CHTIF7 | CTCIF7 | CGIF7 | CTEIF6 | CHTIF6 | CTCIF6 | CGIF6 | CTEIF5 | CHTIF5 | CTCIF5 | CGIF5 | ||||

| w | w | w | w | w | w | w | w | w | w | w | w | |||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| CTEIF4 | CHTIF4 | CTCIF4 | CGIF4 | CTEIF3 | CHTIF3 | CTCIF3 | CGIF3 | CTEIF2 | CHTIF2 | CTCIF2 | CGIF2 | CTEIF1 | CHTIF1 | CTCIF1 | CGIF1 | |

| w | w | w | w | w | w | w | w | w | w | w | w | w | w | w | w | |

Address offset: 0x04

Reset value: 0x0000 0000

Регистр сброса флагов прерывания. Биты данного регистра используются для программного сброса соответствующих битов в регистре флагов DMA_ISR путём записи в бит значения 1, запись в бит 0 не имеет никакого эффекта.

CTEIFx: Channel x transfer error clear

Сброс флага ошибки передачи в канале x.

0: Не имеет эффекта.

1: Сброс флага TEIFx в регистре DMA_ISR.

CHTIFx: Channel x half transfer clear

Сброс флага половинной передачи в канале x.

0: Не имеет эффекта.

1: Сброс флага HTIFx в регистре DMA_ISR.

CTCIFx: Channel x transfer complete clear

Сброс флага завершения передачи в канале x.

0: Не имеет эффекта.

1: Сброс флага TCIFx в регистре DMA_ISR.

CGIFx: Channel x global interrupt clear

Сброс флагов в канале x.

0: Не имеет эффекта.

1: Сброс всех флагов для канала x в регистре DMA_ISR (GIFx, TEIFx, HTIFx и TCIFx).

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | |

| Reserved | ||||||||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| Res. | MEM2 MEM |

PL[1:0] | MSIZE[1:0] | PSIZE[1:0] | MINC | PINC | CIRC | DIR | TEIE | HTIE | TCIE | EN | ||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | ||

Address offset: 0x08+0d20*(x–1)

Reset value: 0x0000 0000

Конфигурационный регистр. Каждый канал имеет свой выделенный конфигурационный регистр, который используется для настройки и включения этого канала DMA.

MEM2MEM: Memory to memory mode

Включение режима "memory to memory" (копирование данных из памяти в память). Бит устанавливается и сбрасывается программно.

0: Режим "memory to memory" отключён.

1: Режим включён.

PL[1:0]: Channel priority level

Уровень приоритета канала. Битовое поле задаётся программно и определяет уровень приоритета канала в соответствии со значениями:

00: низкий;

01: средний;

10: высокий;

11: очень высокий.

MSIZE[1:0]: Memory size

Размер элемента данных в памяти. Битовое поле задаётся программно и определяет размер одного элемента данных, записываемого в память или считываемого из памяти (зависит от выбранного направления передачи) за одну транзакцию:

00: 8 бит (передача по байтам);

01: 16 бит (передача по полусловам);

10: 32 бита (передача по словам);

11: зарезервировано (не используется).

PSIZE[1:0]: Peripheral size

Размер элемента данных для обмена с периферийным устройством. Битовое поле задаётся программно и определяет размер одного элемента данных, считываемого из регистра периферийного устройства или записываемого в него (в зависимости от выбранного направления передачи) за одну транзакцию:

00: 8 бит (передача по байтам);

01: 16 бит (передача по полусловам);

10: 32 бита (передача по словам);

11: зарезервировано (не используется).

MINC: Memory increment mode

Режим инкрементирования адреса в памяти. Этот бит устанавливается и сбрасывается программно.

0: Инкрементирование адреса отключено.

1: Инкрементирование адреса включено.

PINC: Peripheral increment mode

Режим инкрементирования адреса периферии. Бит устанавливается и сбрасывается программно.

0: Инкрементирование адреса отключено.

1: Инкрементирование адреса включено.

CIRC: Circular mode

Циклический режим. Бит устанавливается и сбрасывается программно.

0: Циклический режим отключён.

1: Циклический режим включён.

DIR: Data transfer direction

Направление передачи данных. Бит устанавливается и сбрасывается программно.

0: Чтение данных из периферийного устройства.

1: Чтение данных из памяти.

TEIE: Transfer error interrupt enable

Разрешение прерываний при возникновении ошибок передачи. Этот бит устанавливается и сбрасывается программно.

0: Генерация прерываний при возникновении ошибок передачи отключена.

1: Генерация прерываний при возникновении ошибок передачи включена.

HTIE: Half transfer interrupt enable

Разрешение прерываний при завершении передачи половины данных. Бит устанавливается и сбрасывается программно.

0: Генерация прерываний при завершении передачи половины данных отключена.

1: Генерация прерываний при завершении передачи половины данных включена.

TCIE: Transfer complete interrupt enable

Разрешение прерываний при завершении передачи данных. Бит устанавливается и сбрасывается программно.

0: Генерация прерываний при завершении передачи данных отключена.

1: Генерация прерываний при завершении передачи данных включена.

EN: Channel enable

Включение канала. Бит устанавливается и сбрасывается программно.

0: Канал отключён.

1: Канал включён.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | |

| Reserved | ||||||||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| NDT | ||||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | |

Address offset: 0x0C+0d20*(x–1)

Reset value: 0x0000 0000

NDT[15:0]: Number of data to transfer

Количество элементов для передачи (общее количество транзакций), от 0 до 65535. В этот регистр можно записывать только при отключённом канале. После включения канала, регистр становится доступным только для чтения и содержит оставшееся количество элементов для передачи (или количество транзакций). Это количество в общем случае не равно объёму данных в байтах, т.к. размер одного элемента может быть более одного байта (может быть равным 2 или 4 байтам).

Содержимое регистра уменьшается на 1 после каждой DMA передачи (после каждой транзакции). Когда значение регистра достигает 0, передача останавливается (в нециклическом режиме) или регистр автоматически перезагружается первоначально записанным в него значением и передача продолжается (в циклическом режиме).

Если в регистр записано значение 0, транзакции не выполняются, независимо от того, включен DMA канал или нет.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| PA | ||||||||||||||||||||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | |

Address offset: 0x10+0d20*(x–1)

Reset value: 0x0000 0000

Не допускается запись в регистр при включённом данном канале DMA.

PA[31:0]: Peripheral address

Базовый адрес регистра периферийного устройства из которого выполняется чтение или в который производится запись. Если размер данных периферийного устройства установлен равным 16 бит (PSIZE: 01), доступ осуществляется с автоматическим выравниванием на полуслово (младший бит PA[0] игнорируется). Если размер данных периферийного устройства установлен равным 32 бита (PSIZE: 10), доступ осуществляется с автоматическим выравниванием на слово (два младших бита PA[1:0] игнорируются).

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| MA | ||||||||||||||||||||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | |

Address offset: 0x14+0d20*(x–1)

Reset value: 0x0000 0000

Не допускается запись в регистр при включённом данном канале DMA.

MA[31:0]: Memory address

Базовый адрес памяти, по которому выполняется запись или чтение. Если размер данных в памяти установлен равным 16 бит (MSIZE: 01), доступ осуществляется с автоматическим выравниванием на полуслово (младший бит MA[0] игнорируется). Если размер данных в памяти установлен равным 32 бита (MSIZE: 10), доступ осуществляется с автоматическим выравниванием на слово (два младших бита MA[1:0] игнорируются).