Устройство таймера TIM1

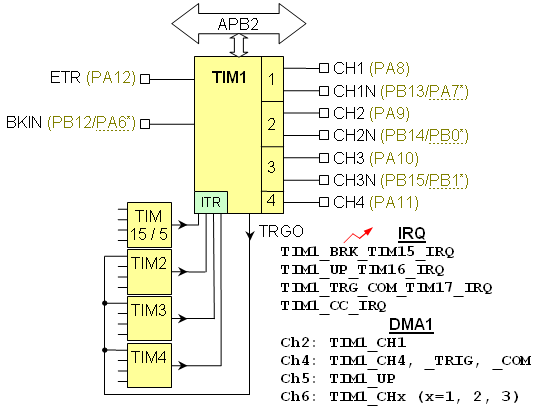

Рассматривая внутреннее устройство таймера, следует упомянуть о том, каким образом он взаимодействует с прочими узлами микроконтроллера.

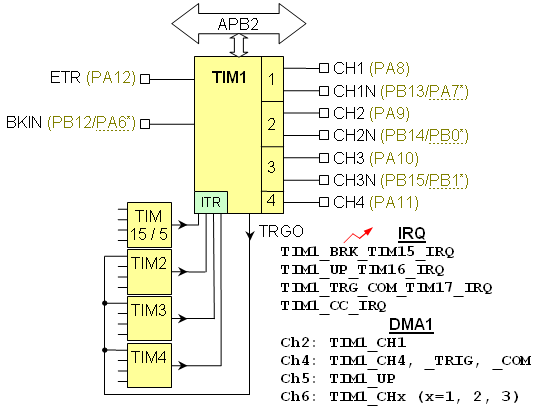

TIM1 является периферийным устройством, которое подключено к шине APB2 микроконтроллера. С этой шины таймер получает тактовый сигнал, который необходим для функционирования данного периферийного устройства, а также может использоваться в качестве внутреннего источника тактового сигнала для счётчика таймера. Следует отметить одну особенность тактирования таймеров по сравнению с прочими периферийными устройствами - если для тактирования шины используется коэффициент деления, отличный от 1, то тактирование таймеров происходит с частотой в 2 раза больше частоты тактового сигнала в шине (т.е. доступные для шины делители 1, 2, 4, 8, 16, с точки зрения функционирования таймера, будут эквивалентны делителям 1, 1, 2, 4, 8).

Рис. %img:env

Таймер имеет выводы, позволяющие ему получать управляющие сигналы и выводить генерируемые им сигналы. Часть выводов задействована во внутренних (внутри микроконтроллера) соединениях, за счёт чего легко организовать взаимодействие между несколькими таймерами. К внутренним относятся выводы для входного триггерного сигнала (ITR0, ITR1, ITR2, ITR3) и вывод для выходного триггерного сигнала (TRGO). Перечисленные входы таймера TIM1 подключены к выходам для триггерного сигнала таймеров TIM15, TIM2, TIM3, TIM4. Если микроконтроллер имеет таймер TIM5, его триггерный выход может быть выбран вместо триггерного выхода таймера TIM15 с помощью функций AFIO. Триггерный выход TIM1 подключён к соединённым вместе входам ITR0 таймеров TIM2, TIM3 и TIM4.

Часть выводов таймера имеет подключение к внешним выводам микроконтроллера, что позволяет организовать взаимодействие таймера с внешними по отношению к микроконтроллеру устройствами. К этим выводам относятся входы/выходы каналов, вход ETR (для внешнего входного триггерного сигнала) и вход BKIN (для входного сигнала защитного отключения). Каждый вывод таймера имеет фиксированную привязку к определённому выводу микроконтроллера. Некоторым выводам таймера назначены два вывода микроконтроллера, по умолчанию используется основной, но с помощью механизма AFIO можно произвести переназначение на дополнительный вывод. На рисунке %img:env для выводов таймера указана выполняемая функция (ETR, BKIN, ...) и в скобках - используемый вывод микроконтроллера, обозначаемый именем, а не номером, так как номер зависит от исполнения корпуса микроконтроллера. При наличии возможности переназначения, дополнительный вывод указан на рисунке через символ "/".

Вывод микроконтроллера, используемый как выход таймера, должен быть сконфигурирован для выполнения альтернативной функции (Alternate Push-Pull или Alternate Open-Drain) - как и в любом случае при работе с периферийными устройствами. Если вывод выполняет функцию входа, никаких дополнительных требований нет.

Таймер TIM1 имеет 4 канала, из них 3 имеют по два выхода - основной (CH1, CH2, CH3) и комплементарный ему (CH1N, CH2N, CH3N), т.е. при работе в режиме выхода, могут использоваться для генерации двух сигналов, изменяющихся в противофазе. Четвёртый канал имеет только один выход, комплементарного не имеет. Выводы CH1, CH2, CH3, CH4 в зависимости от режима работы канала могут быть как входами, так и выходами. Нет необходимости в их физическом разделении, так как всё равно канал не может одновременно работать в режиме входа и выхода. В то же время, за счёт такого совмещения получаем более экономное использование внешних выводов микроконтроллера.

В документации на свой микроконтроллер следует уточнить, к каким его внешним выводам привязаны выводы таймера. Информация для устройств STM32F100x4, x6, x8, xB (например, STM32F100RB) приведена в таблице. В таблице выводы микроконтроллера обозначены через их основную функцию, т.е. номер порта ввода-вывода. Соответствующий номер физического вывода зависит от корпуса микросхемы.

Таблица %tbl:pin

| Вывод таймера |

Вывод микроконтроллера |

Вывод для переназначения |

| TIM1_CH1 |

PA8 |

PE9* |

| TIM1_CH1N |

PB13 |

PA7, PE8 |

| TIM1_CH2 |

PA9 |

PE11 |

| TIM1_CH2N |

PB14 |

PB0, PE10 |

| TIM1_CH3 |

PA10 |

PE13 |

| TIM1_CH3N |

PB15 |

PB1, PE12 |

| TIM1_CH4 |

PA11 |

PE14 |

| TIM1_ETR |

PA12 |

PE7 |

| TIM1_BKIN |

PB12 |

PA6, PE15 |

* PE порт имеется не во всех микроконтроллерах; в случае STM32F100x4..STM32F100xB доступен для устройств в 100-выводных корпусах.

Имеющаяся возможность задействовать таймер для генерации прерываний и запросов DMA делает его особенно мощным, эффективным и гибким инструментом. Если говорить о микроконтроллерах семейства "Medium-density value line devices", в которое входит и мой любимый STM32F100RB, то в них выделено целых 4 прерывания для таймера TIM1 (прочие таймеры имеют по одному вектору, общему для всех событий таймера, сопровождающихся генерацией прерываний). Обработчики имеют следующие имена:

TIM1_BRK_TIM15_IRQHandler

TIM1_UP_TIM16_IRQHandler

TIM1_TRG_COM_TIM17_IRQHandler

TIM1_CC_IRQHandler

Легко заметить особенность в распределении прерываний: из перечисленных прерываний, только TIM1_CC_IRQ выделено исключительно для TIM1, остальные разделяются с другими периферийными устройствами. TIM1_BRK_TIM15_IRQHandler одновременно используется для обработки всех прерываний от таймера TIM15; TIM1_UP_TIM16_IRQHandler используется также для обработки прерываний от TIM16; TIM1_TRG_COM_TIM17_IRQHandler - от таймера TIM17. Особых проблем совместное использование прерываний не вызывает. Во-первых, может оказаться, что используется только одно устройство из числа совместно использующих данное прерывание, тогда и обработчик можно написать так, как будто прерывание используется исключительно одним периферийным устройством. Во-вторых, если всё же оказываются задействованы несколько периферийных устройств, использующих данное прерывание, не составляет никакого труда разделить обработчик на несколько блоков, каждый из которых предназначен для работы со "своим" устройством. Внутри блока проверяем, был ли установлен контролируемый флаг, после чего сбрасываем его и выполняем необходимые действия.

Для обработки запросов DMA используются каналы 2, 4, 5 и 6 устройства DMA1 как указано в следующей таблице (для устройств STM32F100xx).

Таблица %tbl:dma

| Номер канала DMA1 |

Сигнал от TIM1, поступающий на канал |

| 2 |

TIM1_CH1 |

| 4 |

TIM1_CH4

TIM1_TRIG

TIM1_COM |

| 5 |

TIM1_UP |

| 6 |

TIM1_CH3

TIM1_CH2

TIM1_CH1 |

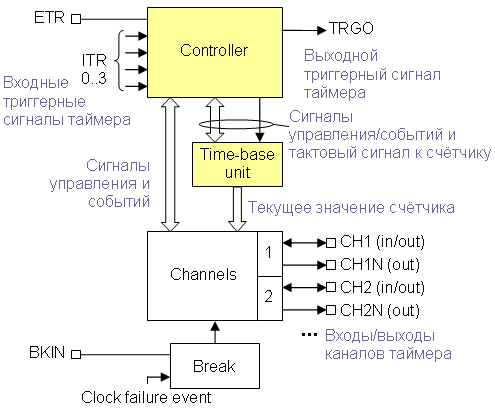

Для эффективного использования таймера необходимо хорошо представлять себе его устройство или, по крайней мере, тех узлов, которые планируется задействовать в работе. Заодно это поможет избежать глупых ошибок и сэкономит массу времени в процессе отладки разрабатываемого устройства.

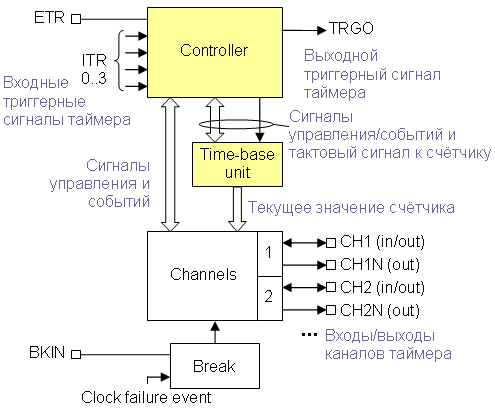

Все универсальные таймеры имеют одинаковую структуру, которая в самом общем виде может быть отображена с помощью схемы (рисунок %img:gen_bd2). Это "крупномасштабная" схема, подробно рассматриваемая в статье "Таймеры в микроконтроллерах STM".

Рис. %img:gen_bd2

Теперь рассмотрим подробно устройство и функции каждого из блоков таймера TIM1. Но прежде, для того, чтобы было проще проследить пути прохождения сигналов между блоками, приведём общую структурную схему таймера. Её нельзя считать полной и абсолютно точной, но она является более детализированной по сравнению с предыдущей.

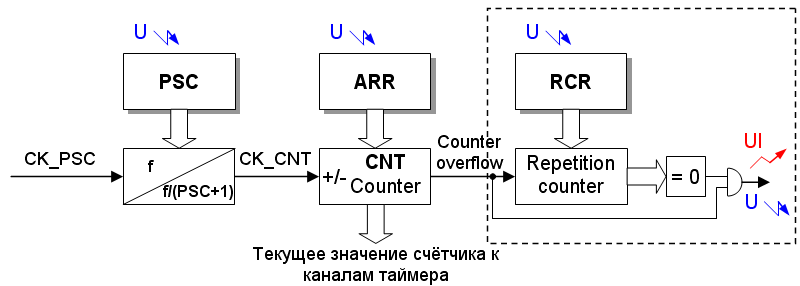

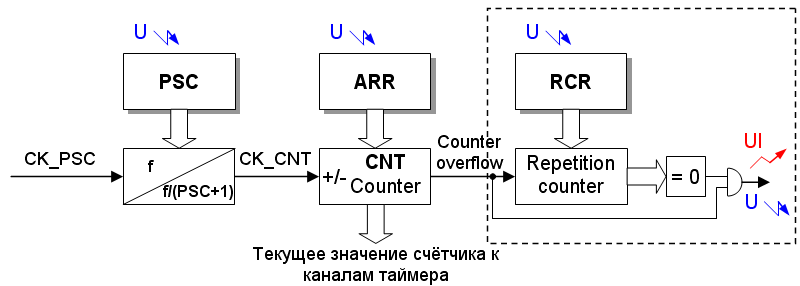

Рис. %img:tim1_bd

Основа таймера - это счётчик, в данном случае 16-разрядный, на вход которого поступает тактовый сигнал CK_CNT. В таймере TIM1 направление счёта (вверх или вниз) может быть задано программно. В любой момент, даже в процессе счёта, содержимое счётчика доступно как для чтения, так и для записи (регистр TIMx_CNT). Тактовый сигнал счётчика CK_CNT формируется с помощью предделителя, который также построен на базе 16-разрядного счётчика, что позволяет задавать коэффициент деления частоты от 1 до 65536. Коэффициент деления определяется значением в регистре TIMx_PSC и равен TIMx_PSC+1. Тактовый сигнал CK_PSC на вход предделителя поступает от выбранного путём программного конфигурирования источника сигнала. В зависимости от настроек, это может быть один из внешних или внутренних сигналов, например сигнал с внешнего вывода, сигнал с шины микроконтроллера или триггерный сигнал от другого таймера.

Рис. %img:tbu

Включение/отключение счёта, выбор направления счёта и другие настройки выполняются с помощью не показанных на этом рисунке регистров управления (регистр TIMx_CR1: бит CEN - разрешение счёта, счёт начинается спустя 1 такт после установки бита CEN; бит DIR - выбор направления счёта и т.д.).

Модуль пересчёта счётчика управляется с помощью регистра автоматической перезагрузки TIMx_ARR. При работе счётчика таймера (CNT) в суммирующем режиме, счёт происходит до значения, содержащегося в регистре TIMx_ARR. Затем, в следующем такте, происходит формирование сигнала переполнения счётчика и одновременно счётчик сбрасывается в 0. В режиме вычитающего счётчика счёт происходит до 0, после чего, в следующем такте формируется сигнал переполнения (в оригинальной документации переполнение при счёте вниз называется антипереполнением) и в счётчик загружается значение из регистра TIMx_ARR. В любом случае модуль пересчёта, т.е. количество состояний, через которые проходит счётчик, равно TIMx_ARR+1. Поэтому частота сигнала переполнения составляет fovr=fCK_CNT/(TIMx_ARR+1). Если TIMx_ARR=0, то счёт останавливается.

Работа в режиме с реверсивным счётом будет описана позже, когда будут подробно рассматриваться различные режимы работы таймера.

Узел, обведённый на рисунке пунктирной линией, имеется не во всех таймерах (но в таймере TIM1 присутствует). Его назначение тесно связано с особенностями генерации события обновления. Поэтому, вначале, несколько слов о событиях обновления.

Некоторые из регистров таймера являются регистрами с предзагрузкой или, иначе говоря, буферизируемыми (из рассматриваемых в этой части статьи - это TIMx_PSC, TIMx_ARR, в каком-то смысле - TIMx_RCR). Это означает, что каждый из этих регистров на самом деле является связкой из двух взаимодействующих регистров. Один из них буферный, именно он является доступным программно, т.е. он непосредственно участвует в операциях чтения и записи. Другой регистр называют активным, так как именно его содержимое управляет функционированием таймера; ещё его иногда называют "теневым" регистром, это название отражает программную недоступность данного регистра - с этой точки зрения он является "тенью" своего буфера, и доступ к нему из программы происходит через буфер. На блок-схемах будем изображать регистры с предзагрузкой в виде прямоугольников с тенью (или с серым фоном), что будет символизировать наличие теневого регистра.

Так вот, при наличии буферизации, содержимое буферного регистра в активный регистр передаётся по особому сигналу, называемому событием обновления. Событие обновления в простейшем случае генерируется при каждом переполнении или антипереполнении счётчика таймера (если счётчик циклов не используется или вообще отсутствует). Польза от всех этих усложнений проявляется при использовании таймера для генерации сигналов, особенно это касается PWM. Независимо от того, как часто мы будем в программе изменять параметры генерируемого сигнала и в какие моменты будем это делать, частота обновления активных регистров будет ограничена частотой событий обновления, а сами обновления привязаны к строго определённым моментам - моментам сброса счётчика таймера. Благодаря этому, при перестройке таймера в процессе генерации, мы избегаем формирования "дефектных" импульсов - укороченных или наоборот, растянутых, даже один из которых может привести к повреждению управляемой силовой части схемы.

Буферизацией некоторых регистров с предзагрузкой можно управлять (из регистров времязадающего блока - это TIMx_ARR; как увидим далее, это относится и к регистрам захвата/сравнения в каналах таймера). Для управления буферизацией TIMx_ARR служит бит ARPE в регистре TIMx_CR1: при нулевом значении бита предзагрузка не используется и записываемое в регистр значение сразу передаётся в активный (теневой) регистр; при единичном значении бита пердзагрузка используется и записываемое в регистр значение попадает сначала в буферный регистр, а передача значения в активный (теневой) регистр происходит тогда, когда наступает событие обновления. Для других регистров с предзагрузкой, например, для TIMx_PSC, не предусмотрено отключение буферизации. Зато предусмотрены механизмы по управлению обновлениями, действующие на все буферизируемые регистры. Можно запретить на некоторое время обновление, установив в 1 бит UDIS в регистре TIMx_CR1. Можно наоборот, принудительно обновить регистры, программно сгенерировав событие обновления записью 1 в бит UG регистра TIMx_EGR.

Если в таймере есть хотя бы один канал с комплементарными выходами, он будет иметь также счётчик циклов со своим регистром автоперезагрузки TIMx_RCR. Данный счётчик полезен при использовании таймера для генерации PWM сигналов, с его помощью можно управлять частотой генерации события обновления: событие обновления возникает при переполнении/антипереполнении счётчика таймера (TIMx_CNT), если при этом счётчик циклов достиг нулевого значения.

Если счётчика циклов в таймере нет (таймер без каналов с комплементарными выходами) или счётчик циклов не используется (TIMx_RCR=0), то событие обновления будет генерироваться при каждом переполнении/антипереполнении счётчика таймера. Если счётчик циклов используется (TIMx_RCR!=0), его значение уменьшается на 1 при каждом переполнении/антипереполнении счётчика таймера. Если счётчик циклов достиг нулевого значения, то очередное переполнение/антипереполнение таймера приведёт к инициализации счётчика циклов начальным значением из его регистра автоперезагрузки TIMx_RCR и генерации события обновления. Частота генерации события обновления будет в TIMx_RCR+1 меньше частоты переполнений счётчика таймера. Так как регистр является 8-битным, значение делителя может изменяться от 1 до 256.

При программной (установка бита UG в регистре TIMx_EGR) или аппаратной (с помощью контроллера подчинённого режима) генерации события обновления, в счётчик циклов немедленно загружается значение из регистра TIMx_RCR.

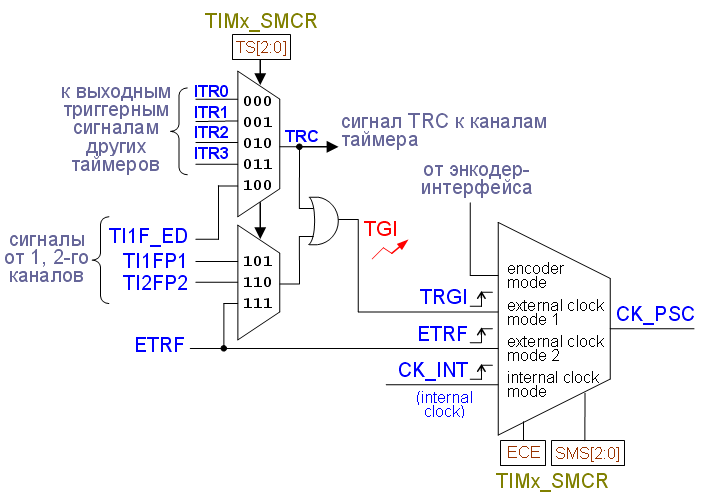

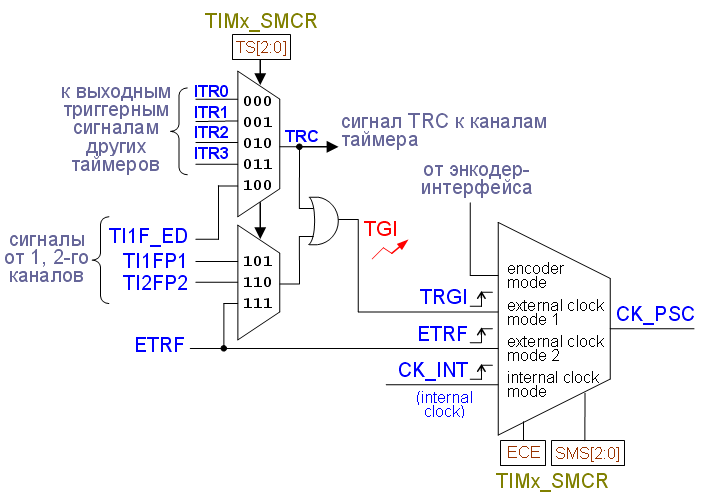

Следующий важнейший вопрос при работе с таймером - выбор сигнала, используемого в качестве тактового сигнала счётчика (CK_PSC). Выбор можно делать из достаточно большого количества вариантов, отвечающая за это часть схемы управления изображена на следующем рисунке (рис. %img:clk).

Вряд ли это может вызвать путаницу, но всё же отметим, что когда мы имеем дело с таймерами, речь может идти о двух разных тактовых сигналах. Во-первых, это тактовый сигнал таймера (как устройства в целом). Он необходим таймеру для работы точно так же, как и любому другому периферийному устройству. Таймер получает его с шины и без него невозможен даже доступ к регистрам устройства. Этот сигнал включается с помощью устройства RCC (после сброса или включения микроконтроллера тактовые сигналы практически всех периферийных устройств отключены для экономии потребления тока). Во-вторых, это тактовый сигнал счётчика, является опорным сигналом, импульсы которого подсчитывает счётчик таймера, и который определяет длительность отмеряемых интервалов времени.

Рис. %img:clk

Самый простой возможный вариант - когда в качестве тактового сигнала счётчика используется тактовый сигнал таймера (тот случай, когда в качестве двух рассмотренных ранее тактовых сигналов используется один и тот же сигнал).

Это не единственный возможный источник внутреннего сигнала, ещё возможно использование одного из входов для триггерного сигнала (ITR0..ITR3) в качестве источника тактового сигнала. Данные входы внутренне подключены к выходам для триггерного сигнала других таймеров.

При решении многих задач требуется использование внешнего сигнала, и такая возможность в таймере TIM1 тоже имеется. Можно использовать сигнал с внешнего триггерного входа ETR или со входа одного из каналов (в данном случае возможно использование только входов первых двух каналов: TI1, TI2). Внешние сигналы подвергаются определённой предварительной обработке, в результате чего получаем сигналы, обозначенные на схеме ETRF, TI1FP1, TI2FP2, TI1F_ED (сигналы подвергаются ресинхронизации, фильтрации, возможна инверсия; TI1F_ED формируется с помощью детектора фронтов). Подробнее об этом в следующем пункте.

За выбор тактового сигнала отвечают биты ECE, SMS[2:0] и TS[2:0] регистра TIMx_SMCR (slave mode control register, регистр управления подчинённым режимом таймера).

Битовое поле SMS[2:0] позволяет включить следующие режимы работы таймера:

- 000: подчинённый режим отключён; используется внутренний тактовый сигнал CK_INT.

- 001..011: режимы 1..3 энкодера; счётные импульсы формируются энкодер-интерфейсом (а также направление счёта).

- 100: Reset Mode, режим сброса - нарастающий фронт сигнала на выбранном триггерном входе (TRGI) сбрасывает счётчик и обновляет регистры.

- 101: Gated Mode, стробирующий режим - таймер выполняет счёт при высоком уровне сигнала на триггерном входе (TRGI); счётчик останавливается (но не сбрасывается) при переходе сигнала на запускающем входе к низкому уровню; таким образом, внешний сигнал управляет как запуском, так и остановкой счётчика.

- 110: Trigger Mode, триггерный режим - счётчик запускается (но не сбрасывается) нарастающим фронтом сигнала на триггерном входе TRGI; в отличие от стробирующего режима (Gated Mode), контролируется только запуск счётчика.

- 111: External Clock Mode 1, режим 1 внешнего тактового сигнала - счётчик тактируется нарастающими фронтами на выбранном триггерном входе (TRGI).

При SMS=0, 0x4, 0x5, 0x6 в качестве тактового сигнала используется внутренний тактовый сигнал CK_INT если ECE=0 и сигнал ETRF, если ECE=1. В режимах SMS=0x4, 0x5, 0x6 входной триггерный сигнал используется для управления таймером (в соответствии с выбранным режимом), источник входного триггерного сигнала выбирается с помощью битового поля TS[2:0].

Значение SMS=0x7 включает режим 1 внешнего тактового сигнала, в котором в качестве тактового сигнала используется входной триггерный сигнал, источник которого также выбирается с помощью TS[2:0]:

- TS[2:0]: Trigger selection

- 000: Internal Trigger 0 (ITR0) - внутренний триггерный сигнал 0.

- 001: Internal Trigger 1 (ITR1) - внутренний триггерный сигнал 1.

- 010: Internal Trigger 2 (ITR2) - внутренний триггерный сигнал 2.

- 011: Internal Trigger 3 (ITR3) - внутренний триггерный сигнал 3.

- 100: TI1 Edge Detector (TI1F_ED) - детектор фронта сигнала TI1.

- 101: Filtered Timer Input 1 (TI1FP1) - сигнал TI1 (после цифрового фильтра).

- 110: Filtered Timer Input 2 (TI2FP2) - сигнал TI2 (после цифрового фильтра).

- 111: External Trigger input (ETRF) - внешний триггерный сигнал ETRF (после цифрового фильтра).

- Примечание.

- Изменять биты данного битового поля допустимо только если оно не используются, т.е. когда SMS=000, в противном случае возможно ошибочное обнаружение фронта при переключении.

- Используются следующие внутренние подключения между входными сигналами ITRx и выходными сигналами TRGO таймеров микроконтроллера:

- ITR0 (TS=000) - подключение к таймеру TIM15 или TIM5 (TIM5 имеется только в линейке "high density value line devices"; в этом случае выбор между TIM5 и TIM15 осуществляется с помощью бита MISC_REMAP в регистре AFIO_MAPR2);

- ITR1 (TS=001) - подключение к таймеру TIM2;

- ITR2 (TS=010) - подключение к таймеру TIM3;

- ITR3 (TS=011) - подключение к таймеру TIM4.

Режимы SMS=0x1..0x3 включают соответствующие режимы энкодера; это весьма специфические режимы, в которых тактовые импульсы счётчика и направление счёта определяются энкодер-интерфейсом.

Бит ECE (external clock enable) используется для включения режима 2 внешнего тактового сигнала. Режим включается установкой бита ECE в 1. В данном режиме в качестве тактового сигнала используется сигнал ETRF - сигнал с внешнего входа ETR после задания активного уровня, прохождения предделителя, цепей ресинхронизации и фильтрации. Используется с SMS=0, 0x4, 0x5, 0x6. Можно заметить, что этот режим аналогичен режиму с SMS=0x7 и TS=0x7, но здесь есть возможность задействовать входной триггерный сигнал (при SMS=0x4, 0x5, 0x6).

Как можно увидеть на схеме, битовое поле TS[2:0] определяет не только источник сигнала TRGI, но также отвечает за выбор источника для сигнала TRC, который может быть задействован для управления каналами таймера. Если битовое поле содержит значения 0..0x4, то в качестве TRC будут использоваться соответственно сигналы ITR0..ITR3, TI1F_ED.

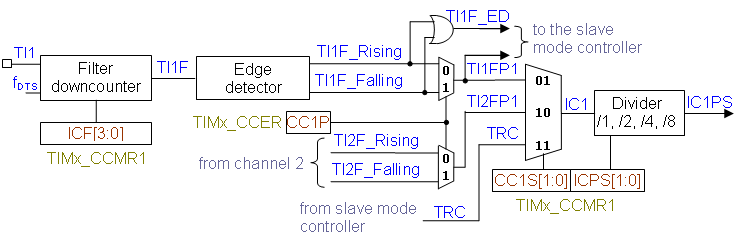

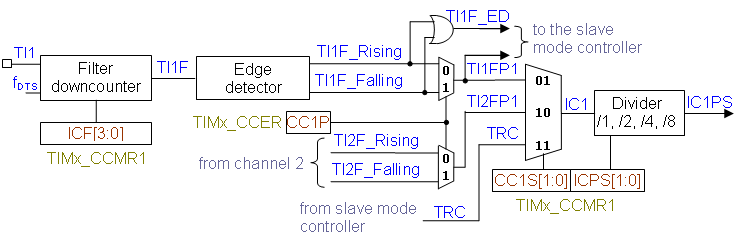

Таймер может использовать следующие внешние сигналы: внешний триггерный сигнал (вход ETR) и сигналы на входах первых двух каналов (TI1, TI2). Как уже говорилось ранее, перед использованием сигналы проходят предварительную подготовку с помощью устройств ресинхронизации, цифровой фильтрации, выделения фронта и др. Рассмотрим блок-схемы цепей, через которые проходят внешние сигналы таймера.

Входные цепи каналов 1 и 2 являются однотипными. Имеется различие лишь в том, что первый канал формирует сигнал TI1F_ED (импульс при обнаружении как переднего, так и заднего фронта сигнала), а во втором канале подобный сигнал не формируется. Ограничимся рассмотрением входа первого канала.

Рис. %img:ch

Первое, что происходит сигналом - это его ресинхронизация, т.е. внешний асинхронный сигнал преобразуется в сигнал, синхронный с тактовым сигналом таймера (подробнее об этом далее). Затем выполняется цифровая фильтрация, если она программно включена в настройках таймера. Управлять фильтром можно с помощью битовых полей IC1F[3:0] (IC2F[3:0] для второго канала) регистра TIMx_CCMR1 - с их помощью задаём частоту сэмплирования входного сигнала и длину цифрового фильтра; по умолчанию фильтр не используется, а частота сэмплирования равна тактовой частоте таймера. Подробнее - на странице с описанием регистров (TIMx_CCMR1). Сигнал, обозначенный на блок-схеме как fDTS - это вспомогательный тактовый сигнал, используемый для формирования защитной паузы в режимах PWM и, в некоторых случаях, как тактовый сигнал для сэмплирования сигналов на внешних входах таймера. fDTS получается из тактового сигнала таймера делением частоты на 1, 2 или 4 (битовое поле CKD[1:0] регистра TIMx_CR1). По умолчанию используется тактовый сигнал таймера.

Фильтр может быть полезен при работе с сигналами, которые проявляют нестабильность вблизи своих фронтов. Выполняемая фильтром функция состоит в том, что он фиксирует факт переключения сигнала только после того, как в течение заданного количества тактов будет последовательно считываться новое значение сигнала.

Итак, с помощью устройств ресинхронизации и фильтрации, из сигнала TI1 получен TI1F. Сигнал TI1F поступает на детектор фронтов, формирующий единичный импульс на одном из выходов - при нарастании входного сигнала, а на другом - при спаде. С помощью бита CC1P регистра TIMx_CCER выбираем, какой из сигналов используется в качестве сигнала TI1FP1: если бит равен 0, в качестве сигнала TI1FP1 используется сигнал обнаружения нарастающего фронта входного сигнала. Сложное название сигнала, TI1FP1, отражает те преобразования, которым подвергнут исходный входной сигнал TI1: суффикс F означает фильтрацию, P1 - означает, что выбор полярности определяется настройками канала 1 (бит CC1P регистра TIMx_CCER).

И уже сигнал TI1FP1 может быть выбран в качестве тактового сигнала для счётчика таймера. Кроме этого сигнала, первый канал формирует сигнал TI1F_ED, который также можно использовать как тактовый сигнал счётчика таймера. Как видно на схеме, TI1F_ED получается в результате логической операции OR над сигналами TI1F_Rising, TI1F_Falling. То есть, на выходе TI1F_ED формируется импульс при обнаружении любого фронта входного сигнала - и нарастающего, и спадающего.

Аналогичным образом канал 2 таймера из входного сигнала TI2 формирует сигнал TI2FP2, который может быть выбран для использования в качестве тактового сигнала счётчика таймера. Сигнал, аналогичный TI1F_ED (в котором единичный импульс генерируется в ответ на любой из фронтов входного сигнала) во втором канале отсутствует.

Структура входной цепи для сигнала ETR существенно отличается от того, что было рассмотрено выше.

Рис. %img:etr

Прежде всего, выбирается активный уровень сигнала или, иными словами, выбирается для дальнейшего использования либо сам сигнал, либо его инверсия (программно управляется битом ETP регистра TIMx_SMCR). После этого сигнал поступает на делитель с управляемым коэффициентом деления частоты. Коэффициент деления задаётся равным 1, 2, 4 или 8 с помощью битового поля ETPS[1:0] регистра TIMx_SMCR. Так мы получаем сигнал ETRP, который в дальнейшем подвергается ресинхронизации и фильтрации.

Принципиальное отличие входа ETR состоит именно в том, что сначала сигнал проходит через делитель, а затем поступает на схему ресинхронизации. Сам делитель является асинхронным устройством, не требует синхронизации входного сигнала с тактовой частотой таймера. В результате, вход ETR может работать с более высокочастотными сигналами, чем входы каналов. Максимальная частота на входе ETR, при выборе коэффициента предделителя равным 8, оказывается в два раза больше частоты тактового сигнала таймера. Это следует из того, что в соответствии с руководством, частота сигнала ETRP (сигнал на выходе предделителя частоты сигнала ETR) не должна превышать 1/4 от тактовой частоты таймера (смотрите описание битового поля ETPS[1:0] регистра TIMx_SMCR).

Здесь уже много раз упоминалось о ресинхронизации, рассмотрим данный вопрос немного подробнее. Таймер является синхронным цифровым устройством (использует тактовый сигнал с шины микроконтроллера). Все остальные сигналы должны быть синхронизированы с тактовым, в противном случае возникнут проблемы, связанные с возможностью перехода в метастабильное состояние, что приводит к довольно неприятным сбоям в работе синхронных схем. Особенно коварны подобные сбои тем, что возникают непредсказуемо и могут быть достаточно редкими, что сильно затрудняет их выявление. При этом устройство длительное время может казаться работоспособным.

Однако, внешние сигналы по своей природе являются асинхронными - их мы получаем от самых различных и, в общем случае, независимых от микроконтроллера источников. Моменты переключения этих сигналов непредсказуемы и невозможно требовать их синхронности с тактовым сигналом микроконтроллера.

Поэтому, в случае использования внешних сигналов, обязательна их ресинхронизация. Естественно, в микроконтроллерах она выполняется. Например, может использоваться классическая схема ресинхронизации из двух каскадно включённых синхронных D-триггеров.

Рис. %img:resync

Первый из триггеров может попасть в метастабильное состояние, если переключение на входе произойдёт в "неудачный" момент. Ситуацию исправляет второй триггер, который каждый раз фиксируется состояние первого триггера на предыдущем такте. И если даже первый триггер попал в метастабильное состояние, маловероятно, что он останется в нём к началу следующего такта.

Не будем здесь подробно рассматривать функционирование схемы, отметим лишь важные особенности её работы. Во-первых, это запаздывание сигнала на выходе относительно входного сигнала - от одного до двух периодов тактового сигнала: первый триггер вносит задержку от 0 до одного периода тактового сигнала (зависит от фазовых соотношений входного сигнала и тактового сигнала) и второй триггер вносит дополнительную задержку на 1 такт. Во-вторых, данная схема имеет ограничение на максимальную частоту входного сигнала. Для того чтобы не происходило пропуска импульсов, как длительность импульса, так и интервал между импульсами должны быть меньше периода тактового сигнала. Это означает, что, например, в случае меандра (коэффициент заполнения 0.5), частота сигнала должна быть менее половины частоты тактового сигнала, а с учётом необходимости иметь запас, зачастую требуют, чтобы частота сигнала не превышала 1/3 части от частоты тактового сигнала. В других случаях, когда коэффициент заполнения не равен 0.5, частота сигнала должна быть ещё ниже.

Смотрите далее:

Устройство каналов таймера. Защитное отключение выходов

author: hamper; date: 2018-03-12